Packaging is emerging as one of the most critical elements in semiconductor design, but it’s also proving difficult to master both technically and economically.

The original role of packaging was simply to protect the chips inside, and there are still packages that do just that. But at advanced nodes, and with the integration of heterogeneous components built using different manufacturing processes, packaging is taking on a much broader and more strategic role. Many of the new packages are application-specific, and they are an integral part of the system architecture. They can help channel heat, improve performance, help to reduce power, and even safeguard signal integrity.

Typically called advanced packaging—to distinguish it from the standard plastic or ceramic type of packaging—this approach has been developed to enhance the reliability of advanced-node chips. In many cases, it also serves as an alternative way to overcome thermal and electrostatic limitations. This is particularly true for multi-chip packages, where a third dimension allows processors to access memories located above them or next to them using very high-speed connections. That can be significantly faster than sending signals from one end of a large chip to the other over skinny wires at 7nm, where heat buildup caused by resistance is problematic. In addition, it allows chip architects to scatter memories throughout the package to avoid contention for resources, which creates routing nightmares for designs with centralized memories.

But packaging is becoming every bit as complicated as developing a complex SoC. While advanced packaging has been ramping up for the past several years in server chips and mobile phones, there is not enough commonality yet for this to be considered mainstream. There are several key reasons for this:

- Most of the companies that have adopted advanced packaging were pushing the limits on performance, but they hit a roadblock with the diminishing power/performance benefits of Moore’s Law. For these companies, cost was less of an issue than performance and form factor.

- Nearly all of the early implementations were custom designs, using non-standard approaches to packaging. This required close collaboration between the chipmakers, the foundries and/or the OSATs. While it has proven effective, particularly for applications such as mobile phones and networking chips, those packages were developed for a specific application using very specific components.

- Most mainstream chipmakers—those not at the leading-edge nodes—still have plenty of power/performance headroom at established nodes, where the vast majority of chips are being developed. This is aided by the fact that foundries have been aggressively adding options at those nodes, which are still significantly less expensive than 10/7nm or even 16/14nm. But as more standardized packaging becomes available, that could change because those companies will be able to mix and match different components.

Consensus about what works where is beginning to emerge. Packaging has been in an almost constant state of change over the past several years as packaging houses and foundries experiment with different ways to put chips together. Even within the same type of packaging approach, such as fan-out, there are chip first and chip last approaches. It’s also possible to add pillars on fan-outs, which add memory stacks on top of logic in a quasi-3D-IC configuration.

And in 2.5D, silicon interposers and organic interposers use a bridge either in the redistribution layer, or in the case of Intel’s Embedded Multi-Die Interconnect Bridge, across various elements to provide a super-fast in-package interconnect between heterogeneous chips.

“The package is now a major part of the operation of the system,” said Joao Geada, chief technologist at ANSYS. “We have reached the end of economic Moore’s Law scaling. When you need to build a big system, instead of throwing everything into a single process, now it’s a question of what’s the most economic process for what I’m trying to achieve. And typically, in a modern system design, that has multiple answers. You can optimize by targeting things to the appropriate process, but that means you still want to preserve the same kind of approximate footprint. And all of that has to be integrated into a single package. This is where all sorts of new challenges come in because the assumptions that a lot of this was built on—that you could make predictions about the behavior of a design in isolation without taking environmental context into account—stop being true.”

In effect, the divide-and-conquer design approach shifts from blocks on the same chip to chips in a package. And while the package reduces some physical effects, such as variation across a large die, it brings its own set of challenges.

“As the variation becomes a larger component of the spec, you have that many more occurrences in the edge of the distribution, and they are additive,” said David Fried, CTO at Coventor, a Lam Research company. “With a 50-core CPU, for example, you’re going to add in all of the standard design complexity with I/Os and memory. But you want to do it faster and the specs and the variation aren’t going away. If those variations don’t shrink commensurately, system engineering becomes that much more difficult. So is it easier if I crack this into five pieces? The system engineering gets a little easier. But it requires heterogeneous integration because you can’t just design everything the way you used to.”

What works where

This has led to a search for the best packaging options, and the amount of research done in this area by systems companies, universities, equipment makers, foundries and packaging houses has been enormous.

“We are seeing the introduction of more advanced system in package (SiP), fan-out on substrate, and 2.5D chip on wafer packages,” said Warren Flack, vice president of worldwide lithography applications at Veeco. “This is on top of the traditional flip-chip market, which continues to show growth.”

The shift toward more advanced packages presents several challenges. For example, high-density fan-out requires tighter pitches with finer redistribution layers (RDLs), which provide the electrical connections in the package. The latest high-density fan-out packages are migrating toward the 1µm line/space barrier and beyond. At these critical dimensions (CDs), fan-outs will provide better performance and cost.

“Redistribution layers with smaller critical dimensions enable reducing the total number of redistribution process levels in a fan-out package,” Flack said. “This, in turn, reduces the total packaging cost and improves yield for our customers. Currently, 1µm RDL is in low volume, but we expect that it will increase significantly over the next few years.”

Going to finer RDL CDs in the package presents some challenges, namely for lithography, which is the art of patterning features on chips and packages.

“Going to smaller features requires exposing with a shorter wavelength (i-line or Hg) and having a larger lens numerical aperture,” Flack said. “The major lithography challenges going forward for these advanced fan-out packages are imaging submicron RDL with high aspect ratios, minimizing overlay errors that occur from die shifting, extremely warped substrate handling, and support for very large 2.5D chip on wafer package sizes. Yield and productivity will drive the cost of adopting advanced fan-out packages. Only very high ASP (average selling price) devices can afford this kind of advanced packaging approach.”

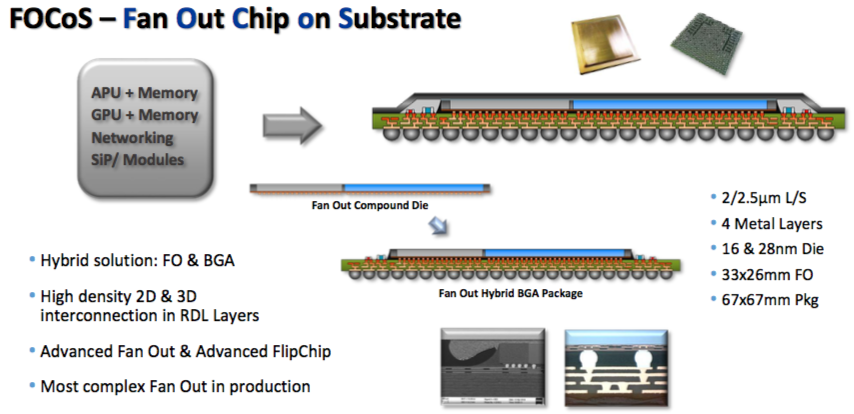

That is expected to continue in the near term, but there are efforts underway to provide the same benefits in fan-outs, and fan-outs with chiplets, as more expensive approaches such as 2.5D where a silicon interposer is currently used. ASE, for example, reports adoption of its fan-out chip on substrate, which can support HBM2 memory. In the past, only 2.5D packages utilized HBM, which are modules of stacked DRAM. ASE has demonstrated the technology for heterogeneous and homogeneous server applications, as well as for AI chips and chiplets.

“This is intended to be an alternative to interposer solutions for these markets,” said John Hunt, senior director of engineering at ASE. “It provides a lower-cost solution, and actually has better electrical and thermal performance than a silicon interposer structure.”

This approach uses a fan-out composite die on a traditional ball-grid array substrate, which is basically the same type of substrate used in standard BGA and 2.5D interposer-based packages. The BGA provides the second level of “fan out” of the package, which is in addition to the finer fan-out chip-on-substrate bump pitch to a standard circuit board assembly pitch.

Fig. 1: Fan-out chip-on-substrate. Source: ASE

Fan-outs continue to be popular in the mobile market, as well. Apple was the first big company to legitimize this approach when it adopted TSMC’s integrated fan-out (InFO) for the iPhone 7. Apple is now working on pillars on top of fan-outs, according to industry sources, to improve performance.

Mobile continues to be the main growth driver for both low-density and high-density fan-outs, but automotive is expected to pick up momentum as the packaging is qualified for automotive grade 1 and 2.

There also are numerous reports of 3D-ICs under development across the industry. Unlike a fan-out, memory is stacked on logic, with connections through the middle of the silicon using through-silicon vias.

TSVs also are being used in silicon interposers, and they are finding a home in silicon photonics, where they are essentially serving as waveguides for optical signals. And while they have not achieved early projections for this market, the market for these types of interconnects is creeping up.

“The projected advanced packaging market growth is accelerating as both logic and memory customers drive adoption of these technologies for improved form factor and performance considerations,” said Manish Ranjan, a managing director at Lam Research. “The initial phase of advanced packaging growth was driven by copper pillar and wafer-level packaging solutions. Customers are now adopting high-density fan-out, silicon interposer, and 3D packaging solutions to provide differentiated system-level performance. The strategic relevance of advanced packaging is validated by the increasing demand from IDMs and system level companies for novel packaging solutions.”

Material alternatives

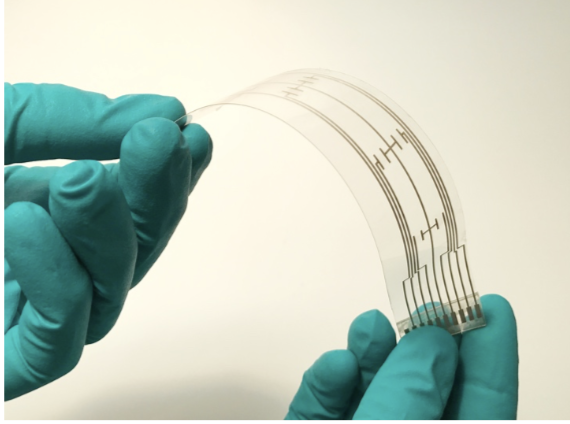

More packaging developments are coming, as well, although not all of them fit under the advanced packaging label. Consider the developments in printed and flexible electronics, for example. In those cases, the packaging may be a flexible substrate or something created using a 3D printer. Rather than etch on silicon, most of these processes are additive.

“You can print with a metal polymer to create a composite that is fused together,” said Ryan Giedd, director/emeritus professor of device engineering at Brewer Science. “That’s more efficient and there is less mass.”

Weight is a major concern in electric vehicles, because the lower the weight the greater the range per charge, and flexible substrates that can stick on like a piece of tape are significantly lighter than a multi-layer printed circuit board with a collection of chips. But this technology is just beginning to gain footing, as well. At this point there are not good physical models to show exactly how these chips behave under a variety of circumstances.

“This is different than silicon-based electronics,” said Giedd. “There are different influences, and each requires a different model. You can’t use off-the-shelf software today.”

Fig. 2: Circuits printed on flexible substrate. Source: Brewer Science

Chiplets

Looming big across the whole packaging space is the chiplet concept, where the basic idea is to create a plug-and-play infrastructure for various components. The idea is to standardize the process in order to reduce costs and enable chipmakers to build systems more quickly.

The first company to adopt this approach was Marvell Semiconductor, which developed a modular chip (MoChi) architecture to allow customers to choose from a menu of features. “We evaluated a lot of technology options and found that the best approach is a standard organic substrate in an MCM (multi-chip module) package” said Yaniv Kopelman, the company’s networking CTO. “This has several advantages. First, all of the OSATs know how to do it. There also is no limit on the number of die, or the placement of those die. And the most compelling feature is that it’s cost-effective. All of the other packaging approaches we looked at were semi-proprietary. The only negative we found was that it’s bandwidth-limited, but we found that to be less significant on big devices.”

There are a number of standards efforts underway in this area. For example, DARPA’s CHIPS program is aimed at simplifying the development of complex chips for a variety of government and commercial applications. In addition, Marvell and Kandou Bus are part of the Ultra Short Reach (USR) Alliance, which is developing a standard way to connect various chiplets together. On top of that, a third group, called the Open Domain-Specific Architecture Workgroup was created last fall. Members of that group include GlobalFoundries, Netronome, Achronix, Kandou, NXP, Sarcina, and SiFive.

“We’re developing a proof of concept,” said Ron Renwick, vice president of products at Netronome. “Netronome is connecting a RISC processor and an FPGA. We also are developing the technical specs for how this will be done, and a business model for how this will work from an IP standpoint. This could be done at the end of June, after which we will demonstrate this concept at the Open Compute Project Summit in Amsterdam in September.”

Conclusion

Packaging is becoming more important and more complicated, but it also is showing signs of settling on various approaches that can help drive down costs. There are concerted efforts to make that happen on a number of fronts, but it’s also not the only path forward.

More talk and activity is also happening around combining technologies that historically haven’t gone together, such as a 5nm or 3nm logic chip packaged with older-node analog and memory components. As Moore’s Law becomes more expensive and time-consuming to pursue, the industry is beginning to limit what gets processed at those nodes. This would mark a big shift in direction, and the implications could be very significant.

Related Articles

Getting Down To Business On Chiplets

Consortiums seek ways to ensure interoperability of hardened IP as way of cutting costs, time-to-market, but it’s not going to be easy.

Lithography Challenges For Fan-Out

Advanced packaging moves into high-volume mobile markets, but requires more sophisticated equipment and lower-cost processes.

Reducing Advanced Packaging Costs

What’s needed to make different packaging approaches more affordable, and why that may not be a critical factor in the short-term.

The Case For Chiplets

Issues in advanced packaging.